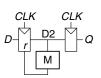

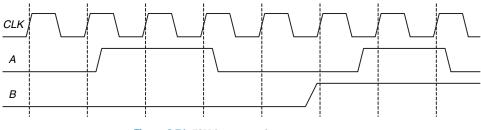

**Exercise 3.1** Given the input waveforms shown in Figure 3.61, sketch the output, *Q*, of an SR latch.

Figure 3.61 Input waveforms of SR latch for Exercise 3.1

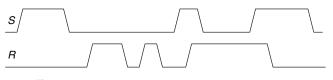

**Exercise 3.2** Given the input waveforms shown in Figure 3.62, sketch the output, *Q*, of an SR latch.

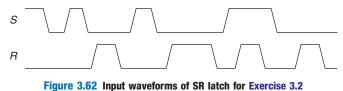

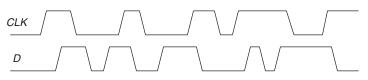

**Exercise 3.3** Given the input waveforms shown in Figure 3.63, sketch the output, Q, of a D latch.

Figure 3.63 Input waveforms of D latch or flip-flop for Exercises 3.3 and 3.5

**Exercise 3.4** Given the input waveforms shown in Figure 3.64, sketch the output, *Q*, of a D latch.

Figure 3.64 Input waveforms of D latch or flip-flop for Exercises 3.4 and 3.6

**Exercise 3.5** Given the input waveforms shown in Figure 3.63, sketch the output, *Q*, of a D flip-flop.

**Exercise 3.6** Given the input waveforms shown in Figure 3.64, sketch the output, *Q*, of a D flip-flop.

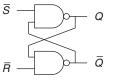

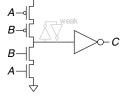

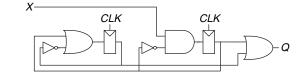

**Exercise 3.7** Is the circuit in Figure 3.65 combinational logic or sequential logic? Explain in a simple fashion what the relationship is between the inputs and outputs. What would you call this circuit?

Figure 3.65 Mystery circuit

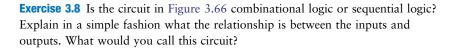

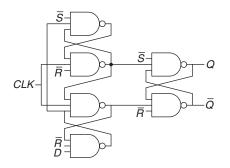

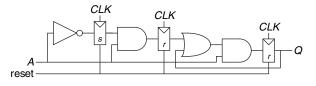

Figure 3.66 Mystery circuit

**Exercise 3.9** The *toggle* (*T*) *flip-flop* has one input, *CLK*, and one output, *Q*. On each rising edge of *CLK*, *Q* toggles to the complement of its previous value. Draw a schematic for a T flip-flop using a D flip-flop and an inverter.

**Exercise 3.10** *A JK flip-flop* receives a clock and two inputs, *J* and *K*. On the rising edge of the clock, it updates the output, *Q*. If *J* and *K* are both 0, *Q* retains its old value. If only *J* is 1, *Q* becomes 1. If only *K* is 1, *Q* becomes 0. If both *J* and *K* are 1, *Q* becomes the opposite of its present state.

- (a) Construct a JK flip-flop using a D flip-flop and some combinational logic.

- (b) Construct a D flip-flop using a JK flip-flop and some combinational logic.

- (c) Construct a T flip-flop (see Exercise 3.9) using a JK flip-flop.

**Exercise 3.11** The circuit in Figure 3.67 is called a *Muller C-element*. Explain in a simple fashion what the relationship is between the inputs and output.

Figure 3.67 Muller C-element

Exercise 3.12 Design an asynchronously resettable D latch using logic gates.

Exercise 3.13 Design an asynchronously resettable D flip-flop using logic gates.

Exercise 3.14 Design a synchronously settable D flip-flop using logic gates.

**Exercise 3.15** Design an asynchronously settable D flip-flop using logic gates.

**Exercise 3.16** Suppose a ring oscillator is built from *N* inverters connected in a loop. Each inverter has a minimum delay of  $t_{cd}$  and a maximum delay of  $t_{pd}$ . If *N* is odd, determine the range of frequencies at which the oscillator might operate.

**Exercise 3.17** Why must *N* be odd in Exercise 3.16?

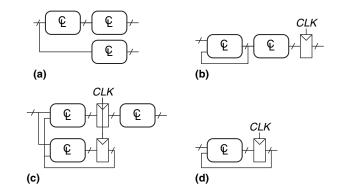

**Exercise 3.18** Which of the circuits in Figure 3.68 are synchronous sequential circuits? Explain.

**Exercise 3.19** You are designing an elevator controller for a building with 25 floors. The controller has two inputs: *UP* and *DOWN*. It produces an output indicating the floor that the elevator is on. There is no floor 13. What is the minimum number of bits of state in the controller?

Figure 3.68 Circuits

**Exercise 3.20** You are designing an FSM to keep track of the mood of four students working in the digital design lab. Each student's mood is either HAPPY (the circuit works), SAD (the circuit blew up), BUSY (working on the circuit), CLUELESS (confused about the circuit), or ASLEEP (face down on the circuit board). How many states does the FSM have? What is the minimum number of bits necessary to represent these states?

**Exercise 3.21** How would you factor the FSM from Exercise 3.20 into multiple simpler machines? How many states does each simpler machine have? What is the minimum total number of bits necessary in this factored design?

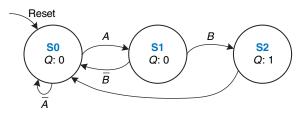

**Exercise 3.22** Describe in words what the state machine in Figure 3.69 does. Using binary state encodings, complete a state transition table and output table for the FSM. Write Boolean equations for the next state and output and sketch a schematic of the FSM.

Figure 3.69 State transition diagram

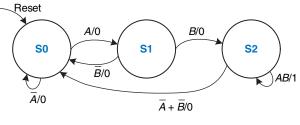

**Exercise 3.23** Describe in words what the state machine in Figure 3.70 does. Using binary state encodings, complete a state transition table and output table for the FSM. Write Boolean equations for the next state and output and sketch a schematic of the FSM.

Figure 3.70 State transition diagram

**Exercise 3.24** Accidents are still occurring at the intersection of Academic Avenue and Bravado Boulevard. The football team is rushing into the intersection the moment light *B* turns green. They are colliding with sleep-deprived CS majors who stagger into the intersection just before light *A* turns red. Extend the traffic

light controller from Section 3.4.1 so that both lights are red for 5 seconds before either light turns green again. Sketch your improved Moore machine state transition diagram, state encodings, state transition table, output table, next state and output equations, and your FSM schematic.

**Exercise 3.25** Alyssa P. Hacker's snail from Section 3.4.3 has a daughter with a Mealy machine FSM brain. The daughter snail smiles whenever she slides over the pattern 1101 or the pattern 1110. Sketch the state transition diagram for this happy snail using as few states as possible. Choose state encodings and write a combined state transition and output table using your encodings. Write the next state and output equations and sketch your FSM schematic.

**Exercise 3.26** You have been enlisted to design a soda machine dispenser for your department lounge. Sodas are partially subsidized by the student chapter of the IEEE, so they cost only 25 cents. The machine accepts nickels, dimes, and quarters. When enough coins have been inserted, it dispenses the soda and returns any necessary change. Design an FSM controller for the soda machine. The FSM inputs are *Nickel*, *Dime*, and *Quarter*, indicating which coin was inserted. Assume that exactly one coin is inserted on each cycle. The outputs are *Dispense*, *ReturnNickel*, *ReturnDime*, and *ReturnTwoDimes*. When the FSM reaches 25 cents, it asserts *Dispense* and the necessary *Return* outputs required to deliver the appropriate change. Then it should be ready to start accepting coins for another soda.

**Exercise 3.27** Gray codes have a useful property in that consecutive numbers differ in only a single bit position. Table 3.23 lists a 3-bit Gray code representing the numbers 0 to 7. Design a 3-bit modulo 8 Gray code counter FSM with no inputs and three outputs. (A modulo N counter counts from 0 to N - 1, then

| Number | Gray code |   |   |

|--------|-----------|---|---|

| 0      | 0         | 0 | 0 |

| 1      | 0         | 0 | 1 |

| 2      | 0         | 1 | 1 |

| 3      | 0         | 1 | 0 |

| 4      | 1         | 1 | 0 |

| 5      | 1         | 1 | 1 |

| 6      | 1         | 0 | 1 |

| 7      | 1         | 0 | 0 |

#### Table 3.23 3-bit Grav code

repeats. For example, a watch uses a modulo 60 counter for the minutes and seconds that counts from 0 to 59.) When reset, the output should be 000. On each clock edge, the output should advance to the next Gray code. After reaching 100, it should repeat with 000.

**Exercise 3.28** Extend your modulo 8 Gray code counter from Exercise 3.27 to be an UP/DOWN counter by adding an *UP* input. If UP = 1, the counter advances to the next number. If UP = 0, the counter retreats to the previous number.

**Exercise 3.29** Your company, Detect-o-rama, would like to design an FSM that takes two inputs, *A* and *B*, and generates one output, *Z*. The output in cycle *n*,  $Z_n$ , is either the Boolean AND or OR of the corresponding input  $A_n$  and the previous input  $A_{n-1}$ , depending on the other input,  $B_n$ :

$$Z_n = A_n A_{n-1} \quad \text{if } B_n = 0$$

$$Z_n = A_n + A_{n-1} \quad \text{if } B_n = 1$$

- (a) Sketch the waveform for Z given the inputs shown in Figure 3.71.

- (b) Is this FSM a Moore or a Mealy machine?

- (c) Design the FSM. Show your state transition diagram, encoded state transition table, next state and output equations, and schematic.

Figure 3.71 FSM input waveforms

**Exercise 3.30** Design an FSM with one input, A, and two outputs, X and Y. X should be 1 if A has been 1 for at least three cycles altogether (not necessarily consecutively). Y should be 1 if A has been 1 for at least two consecutive cycles. Show your state transition diagram, encoded state transition table, next state and output equations, and schematic.

**Exercise 3.31** Analyze the FSM shown in Figure 3.72. Write the state transition and output tables and sketch the state transition diagram. Describe in words what the FSM does.

**Exercise 3.32** Repeat Exercise 3.31 for the FSM shown in Figure 3.73. Recall that the s and r register inputs indicate set and reset, respectively.

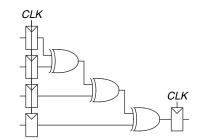

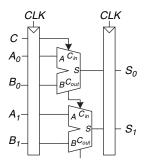

**Exercise 3.33** Ben Bitdiddle has designed the circuit in Figure 3.74 to compute a registered four-input XOR function. Each two-input XOR gate has a propagation delay of 100 ps and a contamination delay of 55 ps. Each flip-flop has a setup time of 60 ps, a hold time of 20 ps, a clock-to-Q maximum delay of 70 ps, and a clock-to-Q minimum delay of 50 ps.

- (a) If there is no clock skew, what is the maximum operating frequency of the circuit?

- (b) How much clock skew can the circuit tolerate if it must operate at 2 GHz?

- (c) How much clock skew can the circuit tolerate before it might experience a hold time violation?

- (d) Alyssa P. Hacker points out that she can redesign the combinational logic between the registers to be faster *and* tolerate more clock skew. Her improved circuit also uses three two-input XORs, but they are arranged differently. What is her circuit? What is its maximum frequency if there is no clock skew? How much clock skew can the circuit tolerate before it might experience a hold time violation?

Figure 3.73 FSM schematic

Figure 3.72 FSM schematic

**Exercise 3.34** You are designing an adder for the blindingly fast 2-bit RePentium Processor. The adder is built from two full adders such that the carry out of the first adder is the carry in to the second adder, as shown in Figure 3.75. Your adder has input and output registers and must complete the addition in one clock cycle. Each full adder has the following propagation delays: 20 ps from  $C_{in}$  to  $C_{out}$  or to *Sum* (*S*), 25 ps from *A* or *B* to  $C_{out}$ , and 30 ps from *A* or *B* to *S*. The adder has a contamination delay of 15 ps from  $C_{in}$  to either output and 22 ps from *A* or *B* to either output. Each flip-flop has a setup time of 30 ps, a hold time of 10 ps, a clock-to-*Q* propagation delay of 21 ps.

- (a) If there is no clock skew, what is the maximum operating frequency of the circuit?

- (b) How much clock skew can the circuit tolerate if it must operate at 8 GHz?

- (c) How much clock skew can the circuit tolerate before it might experience a hold time violation?

Figure 3.75 2-bit adder schematic

**Exercise 3.35** A *field programmable gate array* (*FPGA*) uses *configurable logic blocks* (*CLBs*) rather than logic gates to implement combinational logic. The Xilinx Spartan 3 FPGA has propagation and contamination delays of 0.61 and 0.30 ns, respectively, for each CLB. It also contains flip-flops with propagation and contamination delays of 0.72 and 0.50 ns, and setup and hold times of 0.53 and 0 ns, respectively.

- (a) If you are building a system that needs to run at 40 MHz, how many consecutive CLBs can you use between two flip-flops? Assume there is no clock skew and no delay through wires between CLBs.

- (b) Suppose that all paths between flip-flops pass through at least one CLB. How much clock skew can the FPGA have without violating the hold time?

**Exercise 3.36** A synchronizer is built from a pair of flip-flops with  $t_{\text{setup}} = 50$  ps,  $T_0 = 20$  ps, and  $\tau = 30$  ps. It samples an asynchronous input that changes  $10^8$  times per second. What is the minimum clock period of the synchronizer to achieve a mean time between failures (MTBF) of 100 years?

**Exercise 3.37** You would like to build a synchronizer that can receive asynchronous inputs with an MTBF of 50 years. Your system is running at 1 GHz, and you use sampling flip-flops with  $\tau = 100$  ps,  $T_0 = 110$  ps, and  $t_{setup} = 70$  ps. The synchronizer receives a new asynchronous input on average 0.5 times per second (i.e., once every 2 seconds). What is the required probability of failure to satisfy this MTBF? How many clock cycles would you have to wait before reading the sampled input signal to give that probability of error?

**Exercise 3.38** You are walking down the hallway when you run into your lab partner walking in the other direction. The two of you first step one way and are still in each other's way. Then you both step the other way and are still in each other's way. Then you both wait a bit, hoping the other person will step aside. You can model this situation as a metastable point and apply the same theory that has been applied to synchronizers and flip-flops. Suppose you create a mathematical model for yourself and your lab partner. You start the unfortunate encounter in the metastable state. The probability that you remain in this state after *t* seconds is  $e^{-\frac{t}{\tau}}$ .  $\tau$  indicates your response rate; today, your brain has been blurred by lack of sleep and has  $\tau = 20$  seconds.

- (a) How long will it be until you have 99% certainty that you will have resolved from metastability (i.e., figured out how to pass one another)?

- (b) You are not only sleepy, but also ravenously hungry. In fact, you will starve to death if you don't get going to the cafeteria within 3 minutes. What is the probability that your lab partner will have to drag you to the morgue?

**Exercise 3.39** You have built a synchronizer using flip-flops with  $T_0 = 20$  ps and  $\tau = 30$  ps. Your boss tells you that you need to increase the MTBF by a factor of 10. By how much do you need to increase the clock period?

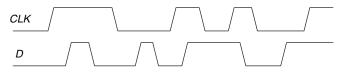

**Exercise 3.40** Ben Bitdiddle invents a new and improved synchronizer in Figure 3.76 that he claims eliminates metastability in a single cycle. He explains that the circuit in box M is an analog "metastability detector" that produces a HIGH output if the input voltage is in the forbidden zone between  $V_{IL}$  and  $V_{IH}$ . The metastability detector checks to determine whether the first flip-flop has produced a metastable output on D2. If so, it asynchronously resets the flip-flop to produce a good 0 at D2. The second flip-flop then samples D2, always producing a valid logic level on Q. Alyssa P. Hacker tells Ben that there must be a bug in the circuit, because eliminating metastability is just as impossible as building a perpetual motion machine. Who is right? Explain, showing Ben's error or showing why Alyssa is wrong.

Figure 3.76 "New and improved" synchronizer